Low Power SoC Design with FlexGen, FlexNoC, Ncore, and CodaCache

Revolutionizing power efficiency in System-on-Chip (SoC) designs with advanced interconnect and cache technologies.

Overview

Overview

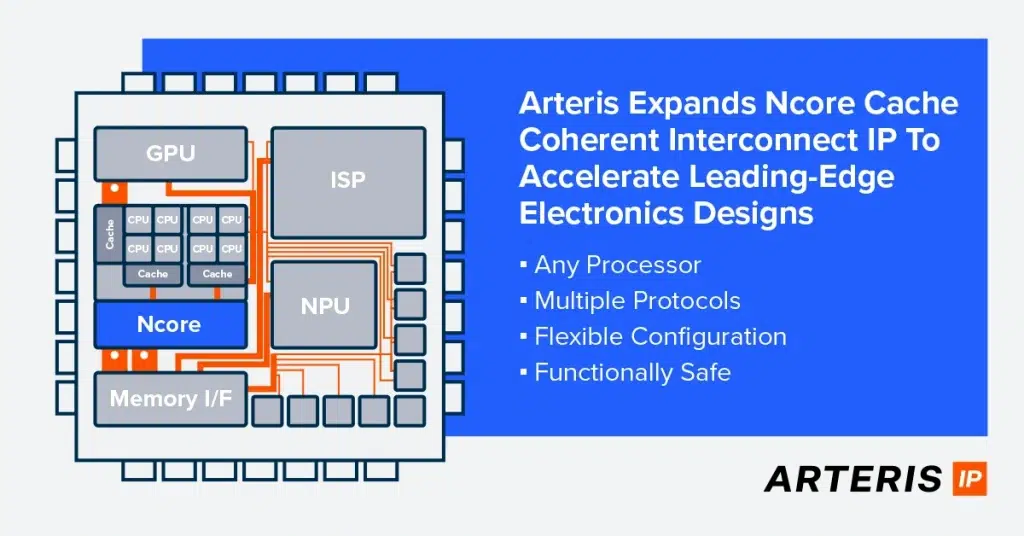

Modern SoC designs face significant challenges in managing power consumption while maintaining high performance and scalability. The growing complexity of integrating multiple processing elements, memory systems, and communication interfaces into a single SoC demands innovative solutions to optimize power efficiency. Arteris offers a comprehensive suite of IP products, including FlexGen, FlexNoC, Ncore, and CodaCache, that address these challenges by providing configurable, high-performance interconnect and cache technologies designed to minimize power usage.

FlexGen and FlexNoC provides a physically aware, non-coherent Network-on-Chip (NoC) interconnect solution that reduces power consumption through optimized interconnects and advanced power management features. Ncore delivers a scalable, cache-coherent interconnect with heterogeneous coherence support, ensuring efficient data sharing and reduced power usage. CodaCache offers a highly configurable last-level cache solution that minimizes main memory accesses, saving power and boosting overall SoC performance. These products enable designers to create low-power, high-performance SoCs suitable for various applications.

Advantages

Advantages

Lorem Ipsum is simply dummy text of the printing and typesetting industry.

Optimized PPA

Arteris’s IP products offer scalable and flexible solutions that can be tailored to meet specific power efficiency requirements. FlexGen and FlexNoC supports various topologies, Ncore allows for configurable snoop filters and proxy caches, and CodaCache offers customizable cache sizes and configurations, enabling designers to optimize power usage based on specific design needs.

Safety

Using Arteris System IP, developers achieve ISO 26262-compliant design, verification, and documentation of safety-critical automotive systems and create ISO 26262-compliant Networks-on-Chip while retaining low-power optimization.

Enhanced SoC Performance

By integrating Arteris’s FlexGen, FlexNoC, Ncore, and CodaCache, SoCs achieve improved performance without compromising power efficiency. These technologies ensure optimal data transfer, reduced latency, and efficient memory access, critical for maintaining high performance in power-constrained environments.

Arteris revolutionizes semiconductor design with

FlexGen - smart NoC IP

FlexGen’s built-in AI/ML-driven automation enables the generation of optimized NoC designs for complex SoCs, delivering expert-level results.

- 10x Productivity Boost

- Expert-Level Results

- Up to 30% Wire Length Reduction

Realize faster time-to-market, optimized power plus performance, and improved overall design economics with FlexGen.

Products

Products

Lorem Ipsum is simply dummy text of the printing and typesetting industry.

Customers

Trusted by innovative companies everywhere

- Architecting the Future of Deep Learning Presentation

- Arm & Arteris AI and ISO 26262 Presentation

- Arm TechCon: Implementing ISO 26262 Compliant AI Systems-on-Chip with Arm and Arteris

- Automating the Generation of Scalable and Reusable FMEDA in Complex Systems-on-Chip (SoCs)

- Building Better IP with RTL Architect NoC IP Physical Exploration

- Challenges Adopting Fault Injection to Support Safety Analysis in Complex SoCs

- Efficient Scaling of AI Accelerators Using NoC Tiling

- FMEDA Automation for Scalability and Reuse in Complex Systems on Chips (SoCs)

- Fundamentals of ISO 26262 Part 11 for Semiconductors

- Implementing Low-Power AI SoCs Using NoC Interconnect Technology

- Implementing Machine Learning & Neural Network Chip Architectures

- Is the Missing Safety Ingredient in Automotive AI Traceability?

- ISO 26262 System-on-Chip (SoC) Safety Analysis for ADAS and AV

- ISO 26262: FMEA before FMEDA

- ISO 26262: What to Expect From Your Chip or IP Provider

- Lessons Learned Integrating AI/ML Accelerators into Complex ISO 26262 Compliant Systems-on-Chip

- Routing Congestion: The Growing Cost of Wires

- Safety Considerations for Network-on-Chip (NoC) Development

- The Role of Networks-on-Chips Enabling AI/ML Silicon and Systems

- Tiled Approach to System Scaling

- Using Synopsys Z01X to Accelerate the Fault Injection Campaign of a Fully Configurable IP

- EE Journal: Managing the Massive Data Throughput: AI-Based Designs and The Value of NoC Tiling

- Electronic Design: All About NoCs

- SemiWiki: The Impact of Arteris on Automotive and Beyond with Frank Schirrmeister

- SemiWiki: A Broad View of Design Architectures and the Role of the NoC with Arteris’ Michal Siwinski

- EE Journal: The Freedom to Innovate: Arteris and the Rise of RISC-V

- EE Journal: The Network-on-Chip Pioneer: How Arteris Enabling SoC Developers to Create Physically Valid NoCs Faster

- A Design Flow for Critical Embedded Systems

- A Power Consumption Estimation Approach for Embedded Software Design using Trace Analysis

- AMS System-Level Verification and Validation using UVM in SystemC and SystemC-AMS: Automotive Use Cases

- Fundamentals of Semiconductor ISO 26262 Certification: People, Process and Product

- How to Efficiently Achieve ASIL-D Compliance Using NoC Technology

- Optimizing Enterprise-Class SSD Host Controller Design with Arteris FlexNoC Network-On-Chip Interconnect IP

- Power Dissipation of the Network-on-Chip in a System-on-Chip for MPEG-4 Video Encoding

- Re-Architecting SoCs for the AI Era

- Routing Congestion: The Growing Cost of Wires

- Scalability – A Looming Problem in Safety Analysis

- Security in Artificial Intelligence

- Using Machine Learning for Characterizations of NoC Components

- Using Synopsys Z01X to Accelerate the Fault Injection Campaign of a Fully Configurable IP

- Using Virtual Prototypes to Improve the Traceability of Critical Embedded Systems Flow

- Boost SoC Efficiency and Speed with FlexGen Smart NoC IP Automation White Paper

Latest News