Magillem Registers

Faster Time to Market With an Error-Free System Memory Map

Overview

Enabling Effective Hardware/Software Interface Development for Schedule Acceleration

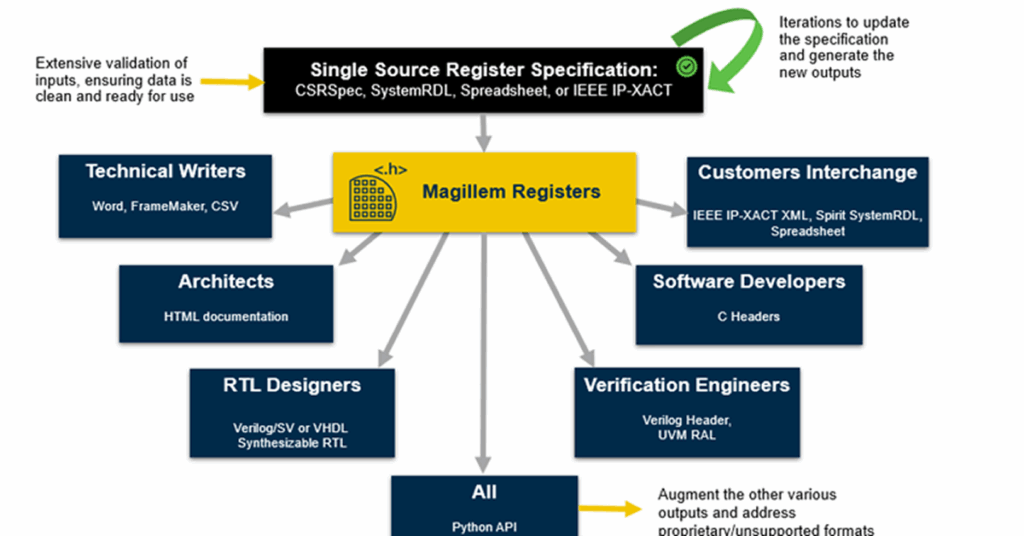

Magillem® Registers offers a single source of truth methodology, which not only targets the traditional need to manage registers, but also addresses today’s HW/SW integration challenges for large-scale SoCs.

Magillem Registers enables quick and scalable automated implementation, cutting the time to market for the Hardware/Software Interface (HSI) generation in half.

Straightforward Register Intent Capture

Magillem Registers translates the specification of registers into executable design code by automatically importing the register descriptions from different sources and formats.

- Automatically checks the accuracy of the information (overlaps, configurability, reserved empty spaces, …).

- Enables close collaboration between HW, SW, and tech doc teams through a single source of truth methodology for consistently generated data.

- Comprehensive HSI automation ensures better quality design and faster productivity.

Straightforward Register Intent Capture

Automatically Generate Consistent Data

Automatically Generate Consistent Data

It is a true cross-compiler with over 1,000 functional, behavioral, syntactic, and semantic error checks. It supports various formats and generates multiple outputs simultaneously.

Generated data is consistent and complete, which allows the verification team to have an up-to-date generated register model to work from.

Error-Free System Map Generation

Synchronizing connectivity and memory map information with full integration of Magillem Registers and Magillem Connectivity:

- Calculate and display the system map from the selected initiator.

- Confirm that memory regions defined in the memory map can be reached (presence of a physical path).

- Check that all the SW visible elements (registers or memory regions) in connected targets are present in the memory map.

Error-Free System Map Generation

Features

Magillem Registers Key Features

- Single Database: Import and capture memory map information into a single database for generating RTL, digital verification, firmware, and documentation

- Various input formats: CSRSpec language, SystemRDL, IP-XACT 2009/2014/2022, spreadsheets…

- Extensive error/syntax checking: with over 1,000 error checks

- Alternative UVM backdoor methodology: for high performance on large designs

- Advanced features: Registers broadcast/alias, virtual registers, wide memories and atomic access support

- Tool Integration: Tight link with the connectivity tool to generate a system address map when both tools are combined

Explore additional features of Magillem Registers, download the datasheet.

NoC Integration Automated Flow

Automated flow to leverage SoC connectivity information:

- Improved productivity with reduced process

- Better quality with early errors detections thanks to the checkers

NoC Integration Automated Flow

Benefits

Magillem Registers Product Benefits

Easy Specification Adjustment

Very fast iteration with updated information across design teams ensuring data consistency

Agile Design Process

Ensure best practices and early engagement of the entire design team

Scalable & Expansive

Compile over 5 million registers plus use on large-scale SoC memory maps

Automated & Efficient

Reduce tedious and error-prone tasks with fully-automated flow and shorten the overall process

Accurate & Consistent

Count on a single source of truth with HW, SW and documentation all in sync to ensure accuracy and cross-team consistency

Quality Assurance

Catch errors at the data entry stage with the memory map information before running any simulation

Productivity Booster

Accelerate the schedule with a correct-by-construction SW interface

Options

Magillem Registers Product Options

Seamlessly Integrated Extensions to the Base Feature Set

- Automatically create the entire IP-XACT platform from the xls file input describing the system map

- Automatically create the entire IP-XACT platform from the xls file input describing the system map

- Enable keeping both software and hardware ends synchronized

- Single/Double Error Detection: register byte parity bit and register duplication

- SW and HW Interface Protection: AMBA check types

- Error reporting: error output bits and protocol error signaling

- Ensure support of safety requirements for automotive industry

Arteris accelerates AI-driven silicon innovation with its expanded multi-die solution

Foundational technology for rapid chiplet-based design.

- Flexible design scalability

- Differentiated AI performance

- Aligned with evolving industry standards

Built on silicon-proven NoC IP and Magillem™ automation to scale modular architectures, simplify multi-die projects, and compress development schedules.

Support and Training

Need Help?

Support and Services

Arteris provides world-class design support and services to our customers and partners.

Training

Unlock the full potential of Arteris products. Explore customized learning solutions designed to boost your expertise.

Arteris Academy

Learn at your own pace, on your schedule. Access our library of on-demand training modules and develop new skills today.

Arteris SoC Integration Automation with the Magillem Platform

Learn about the powerful combination with Magillem Connectivity and Magillem Packaging.

| Category | Features | Magillem Packaging | Magillem Connectivity | Magillem Registers |

|---|---|---|---|---|

| IP-XACT Conversion | 2009 to 2022 | |||

| 2014 to 2022 | ||||

| Resource Management | Projects | |||

| Catalogs | ||||

| Components | ||||

| TGI | TGI API | |||

| HDL Import | Verilog/SystemVerilog support | |||

| View & FileSet elaboration | ||||

| Bus Interface | Auto mapping | |||

| Rules Checkers | Design and component | |||

| Memory and system map | ||||

| Configurable checker severity | ||||

| Assembly | Rule-based connectivity | |||

| Bus/signal split/tie/open/feedthrough | ||||

| Glue logic insertion | ||||

| RTL Netlist Generation | Configurable header | |||

| Keep parameter expressions | ||||

| Signals/netname/tie management | ||||

| Hierarchical Manipulations | Merge, Flatten, Move operations | |||

| Parameter propagation | ||||

| IP Update | Rename/resize/delete/merge | |||

| User mapping rules definition | ||||

| Diff and Merge | Accept/Reject any change | |||

| Conflict resolution wizard | ||||

| Import Memory Map Description | SystemRDL support | |||

| IP-XACT support | ||||

| Excel spreadsheets support | ||||

| Generate HSI Outputs | RTL register bank (VHDL, Verilog, SystemVerilog) | |||

| Customized C Header files | ||||

| UVM RAL files | ||||

| Documentation (Word, FrameMaker, HTML) | ||||

| SystemRDL description | ||||

| IP-XACT description |

Resources

Resources

Lorem Ipsum has been the industry’s standard dummy text ever since the 1500s, when an printer.

- Architecting the Future of Deep Learning Presentation

- Arm TechCon: Implementing ISO 26262 Compliant AI Systems-on-Chip with Arm and Arteris

- Automating the Generation of Scalable and Reusable FMEDA in Complex Systems-on-Chip (SoCs)

- Implementing Machine Learning & Neural Network Chip Architectures

- Modernizing the Hardware / Software Interface – Life Beyond Spreadsheets

- A Configurable Test Infrastructure using a Mixed-Language and Mixed-Level IP Integration IP-XACT Flow

- A SystemC Extension for Enabling Tighter Integration of IP-XACT Platforms with Virtual Prototypes

- AMS System-Level Verification and Validation using UVM in SystemC and SystemC-AMS: Automotive Use Cases

- Building a Portable Stimulus Flow Based on Magillem IP-XACT Packaging

- Generation of UVM Compliant Test Benches for Automotive Systems using IP-XACT with UVM-SystemC and SystemC AMS

- HW / SW Interface Generation Flow Based on Abstract Models of System Applications and Hardware Architectures

- Scalability – A Looming Problem in Safety Analysis

- Using Virtual Prototypes to Improve the Traceability of Critical Embedded Systems Flow

Latest News