Semiconductor Engineering: System Integration With Standards-Based Automation

- Insaf Meliane

- 2 min read

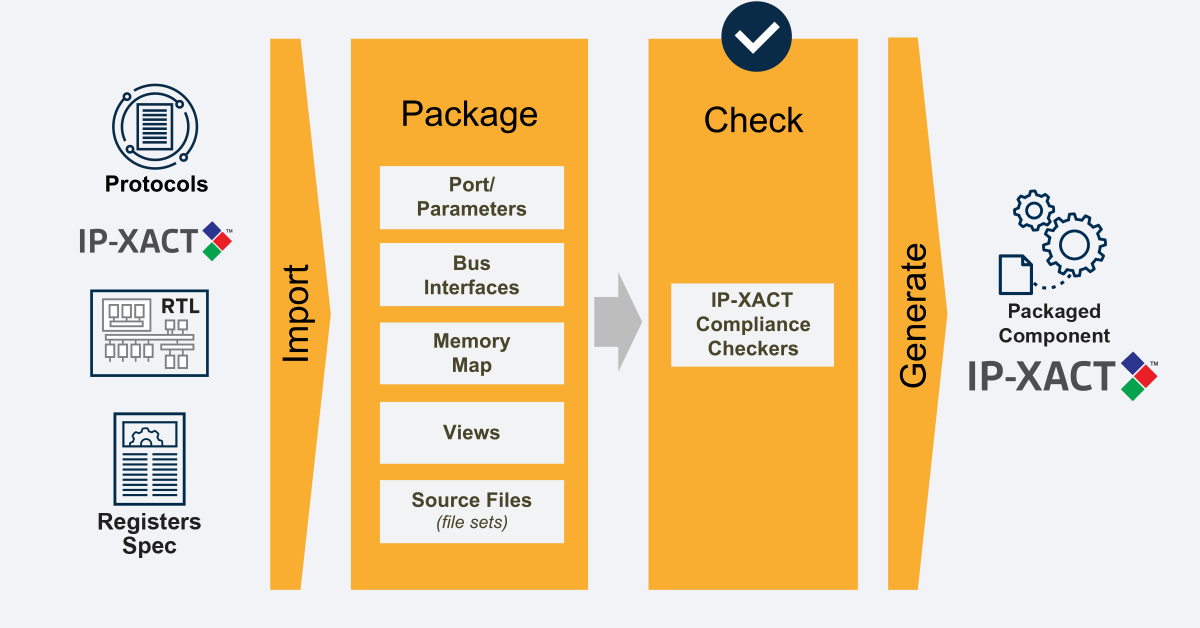

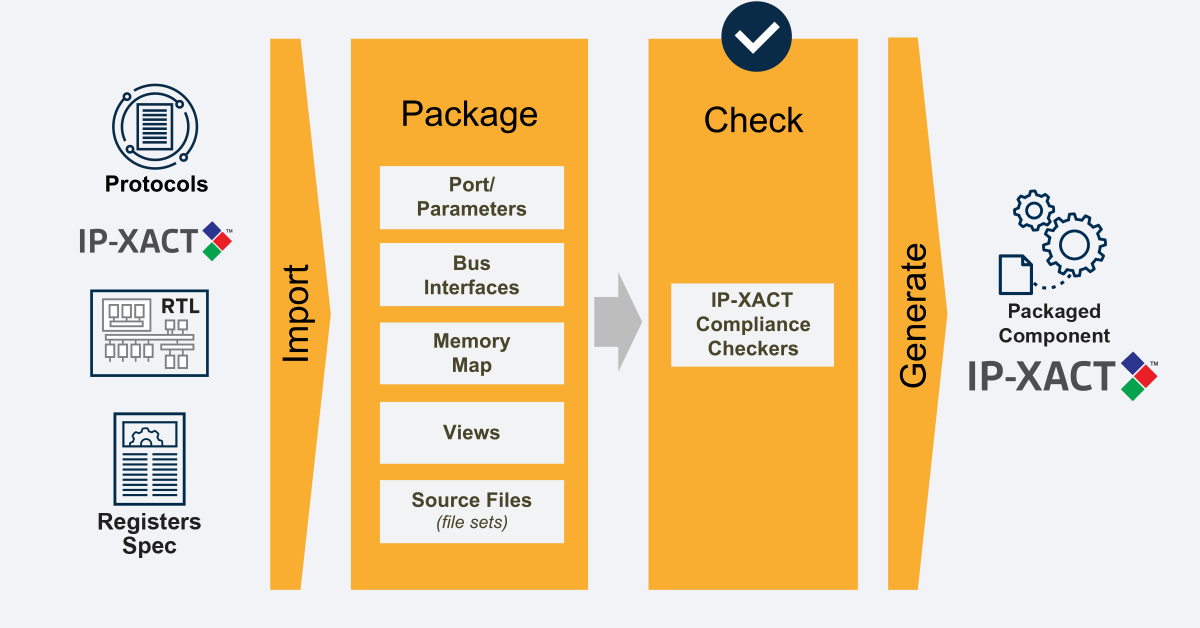

A structured approach ensures consistent IP metadata representation across abstraction levels, design tools, and development teams.

Today’s semiconductor designs support a broad range of applications, from mobile and edge devices to AI accelerators and data center systems. To keep pace, design teams are shifting from monolithic systems-on-chip (SoCs) to increasingly complex multi-die and chiplet-based architectures. These heterogeneous systems often incorporate IP developed at different times, by different teams, or sourced from third parties. Managing this complexity requires a structured, standards-based approach that ensures consistent metadata representation across abstraction levels, design tools, and development teams. Without such a foundation, the benefits of scalable IP reuse and efficient integration are difficult to achieve, even when using proven IP blocks.

Most SoCs incorporate a mix of soft IP blocks and hard IP components sourced from multiple vendors, along with internally developed IPs. This proprietary customization is often what differentiates one product from another. While this approach accelerates development and leverages existing expertise, it also introduces complications. Each IP may come with its own naming conventions, documentation formats, and assumptions about integration, making the process of putting everything together slow and error-prone.

The task becomes even more challenging when assembling IP from different sources into a unified, top-level system. Design teams must manually interpret and reconcile inconsistent port definitions, parameter sets, memory maps, and bus interfaces. Critical metadata is often buried in spreadsheets or plain-text documentation, leaving room for misinterpretation and integration mistakes. As systems scale, the lack of a consistent structure and automation-friendly format becomes a bottleneck for both verification and reuse.

A structured foundation for scalable IP integration

A more effective solution begins with a standard, machine-readable way to describe IP components that supports both individual block integration and system-level assembly. This description should include all relevant interface information, from bus protocols to register maps, and it must be flexible enough to support a range of abstraction levels. This foundation enables scalable automation and reduces integration risk.

To read the full article on SemiEngineering, click here.