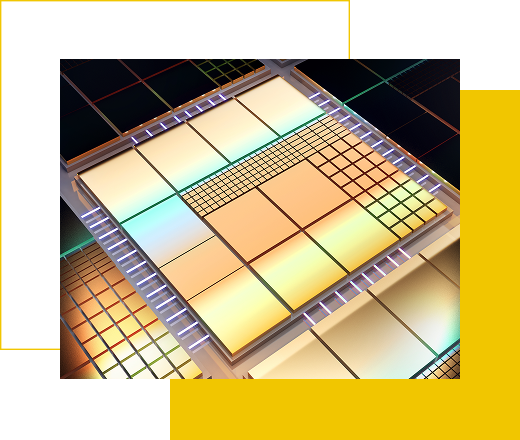

Multi-Die Designs

Upgrade your data transport from Networks-on-Chips (NoCs) to Super-NoCs distributed across multiple chiplets

Overview

Overview

The insatiable drive toward higher performance and integration for semiconductor devices is propelling adoption of multi-die systems and chiplet-based designs—pushing Moore’s Law into the “More-than-Moore” era. Traditional monolithic chips can no longer satisfy the escalating demands of today’s complex, high-performance computing and AI workloads.

Arteris accelerates that AI-driven silicon innovation with its expanded multi-die solution. Built on silicon-proven NoC technology and Magillem™ automation, the platform delivers flexible design scalability, differentiated AI performance, and alignment with evolving industry standards.

Working with industry standards such as Arm AMBA, and with ecosystem partners that supply die-to-die PHYs—whether Universal Chiplet Interconnect Express™ (UCIe), Bunch of Wires (BoW) or proprietary links—Arteris NoC IP ensures seamless, low-latency data flow between chiplets so developers can hit aggressive performance, power and time-to-market goals despite the growing complexity of multi-die designs.

Advantages

Advantages

Lorem Ipsum is simply dummy text of the printing and typesetting industry.

Interoperability

Connect to industry-leading die-to-die PHY connections using their digital controllers using standard interfaces like Arm AMBA protocols.

Bandwidth

Increase on-chip and off-chip bandwidth with HBM2 and multichannel memory support, multicast/broadcast writes, VC-Link™ Virtual Channels, and source-synchronous communications.

Low Power

Fewer wires and fewer gates consume less power, breaking communication paths into smaller segments allows to power only active segments, and simple internal protocol allows aggressive clock gating.

Multi-Die Use-Cases

Homogeneous Scale-Out

Demand for larger, scalable systems is driving the requirement for homogeneous solutions which enable a single chiplet design to be re-used multiple times to scale up to a larger system. A homogeneous chiplet solution may be selected because the design is too large for a reticle (858mm2) or yield issues would make a single die solution prohibitively expensive compared with multiple smaller dies with improved yield.

Heterogeneous Disaggregation

Standards

Standards

From a system design perspective, choosing the proper NoC protocol for the die-to-die data transport is critical to meeting performance, latency, and power requirements. Providers of the physical connections typically deliver PHYs and Controllers, including Link Layers that carry the raw Flow Control Units (FLITs) from die to die.

Arteris already works with partners like Synopsys, Cadence, Alphawave, Blue Cheetah Analog, Innosilicon, and others to align on NoC to Controller/PHY interfaces. In addition, Arteris actively participates in the related standardization efforts. Specifically, Arteris actively engages in the following standardization efforts:

Products

Products

Lorem Ipsum is simply dummy text of the printing and typesetting industry.

- Architecting the Future of Deep Learning Presentation

- Arm & Arteris AI and ISO 26262 Presentation

- Implementing Low-Power AI SoCs Using NoC Interconnect Technology

- Implementing Machine Learning & Neural Network Chip Architectures

- Routing Congestion: The Growing Cost of Wires

- The Role of Networks-on-Chips Enabling AI/ML Silicon and Systems

- Tiled Approach to System Scaling

- A Configurable Test Infrastructure using a Mixed-Language and Mixed-Level IP Integration IP-XACT Flow

- Fundamentals of Semiconductor ISO 26262 Certification: People, Process and Product

- How to Efficiently Achieve ASIL-D Compliance Using NoC Technology

- Mobileye Case Study: Using Arteris for ADAS

- Re-Architecting SoCs for the AI Era

- Routing Congestion: The Growing Cost of Wires

- Scalability – A Looming Problem in Safety Analysis

- Security in Artificial Intelligence

- Using Machine Learning for Characterizations of NoC Components

- Using Virtual Prototypes to Improve the Traceability of Critical Embedded Systems Flow

- Making Cache Coherent SoC Design Easier with Ncore

Latest News