Ncore Cache Coherent Interconnect IP

High-Bandwidth, Low-Latency Network-on-Chip Interconnect

Overview

Solving Multi-Core Design Challenges

With Safety Support

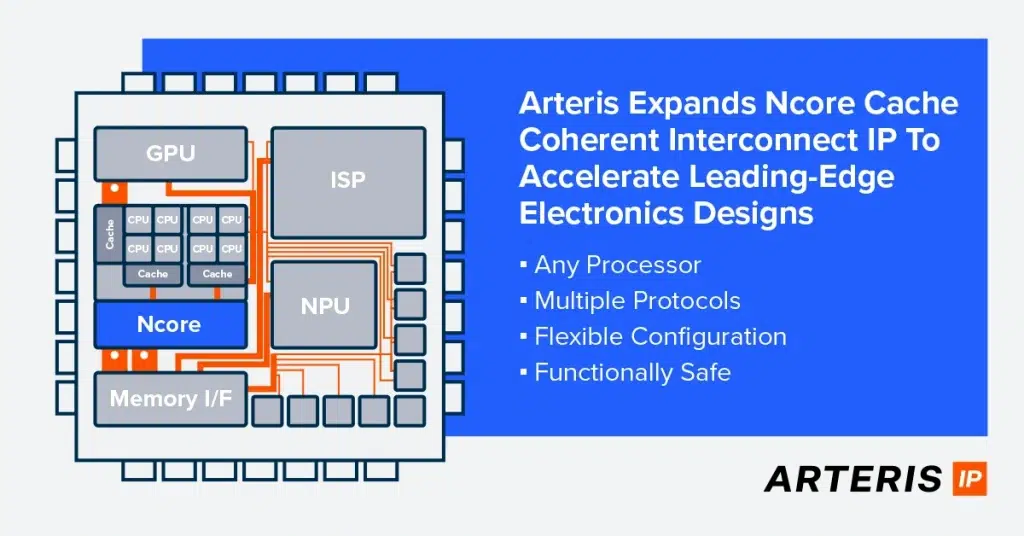

Arteris accelerates AI-driven silicon innovation with its expanded multi-die solution. Ncore™—our silicon-proven coherent Network-on-Chip IP—now extends full cache-coherency across chiplets, giving designers foundational technology for rapid, modular innovation.

Built on more than a decade of volume silicon, Ncore™ is highly configurable, power-efficient and works with any processor, including Arm® and RISC-V.

It is ISO 26262 ASIL D -ready and pairs with Magillem™ automation for IP integration software, so teams can scale modular architectures, simplify multi-die design and compress development schedules.

Ncore and FlexNoC together deliver unparalleled performance optimisation, scalability and system integration, enabling robust cache-coherence , efficient communication, and flexibility, leading to market differentiation and accelerated time-to-market. inside a die or across chiplets.

Advantages

The Only Multi-Processor, Multi-Die, Multi-Protocol, Highly Configurable Cache Coherent NoC

Empowers SoC developers to create high-performance coherent SoC

Scalable

Ncore provides a high-bandwidth, low-latency interconnect fabric for efficient communication between different components of an SoC and between multiple dies, offering scalable performance and power efficiency from small embedded systems to large multi-billion transistor and multi-die designs.

Configurable

Multi-protocol coherency gives choice and reuse for legacy and future IP support. CHI-E, CHI-B, and ACE coherent as well as ACE-Lite I/O coherent agent interfaces allow multiple initiator IPs to be connected to the same Ncore. Ncore also enables AXI non-coherent agents to act as I/O coherent agents.

Safe

ISO-certified by an external assessor to ensure Ncore readiness for use in ISO 26262 -compliant chips from ASIL B to ASIL D, enabled by the Ncore Safety and Reliability product option. Automated generation of Fault Modes Effects and Diagnostic Analysis (FMEDA) data for your Ncore configuration.

Features

Ncore Key Features

- Highly scalable system

- True heterogeneous coherency with mixed AMBA CHI and AMBA ACE support

- Full coherency for cached processors and I/O coherency for accelerators

- Multi-die cache coherency over UCIe™ 1.1 via an AMBA CXS.B interface — up to four chiplets, and up to 4 × 64 GB/s links per die*

- Configurable network and topologies

- Mesh topology with physical tiling of repetitive blocks*

- Functional safety with FMEDA generation and ASIL D certification*

- Configurable snoop filters

- I/O proxy cache and system memory cache

- Low power consumption

- Quality of Service (QoS)

- Debug & trace/monitoring

* Denotes product option

Explore additional features of Ncore, download the datasheet.

Feature Spotlight

NoC Tiling — new feature with Ncore

NoC tiling with mesh topology for cache coherent CPUs. Up to 256 CPUs with 32-core cluster size.

- Scale performance

- Condense design time

- Speed testing

- Reduce design risk

- Supports Arm and RISC-V architectures

Create modular, scalable designs, enabling faster integration, verification and optimization.

Benefits

Ncore Product Benefits

Higher Frequencies, Lower Latencies

Use of multiple configurable snoop filters to accommodate different cache organization

Lower Power Consumption

Fewer off-chip main memory accesses resulting in lower power consumption

Smaller Die Area

Fewer wires using optimal NoC transport layer

Easy Configuration

Ncore adapts to each coherent agent’s behavior and characteristics

Faster Time to Market

Tiling accelerates physical design, implementation and timing closure

Flexible Topologies

Choose from crossbar, mesh and ad-hoc topologies

Safety

Automate FMEDA safety documentation, ISO26262 ASIL B to D certified

Automated Verification

Saving hundreds of hours of work over manual verification generation

Shorter Schedules

Fewer iteration loops

Options

Ncore Product Options

Lorem Ipsum is simply dummy text of the printing and typesetting industry.

Arteris accelerates AI-driven silicon innovation with its expanded multi-die solution

Foundational technology for rapid chiplet-based design.

- Flexible design scalability

- Differentiated AI performance

- Aligned with evolving industry standards

Built on silicon-proven NoC IP and Magillem™ automation to scale modular architectures, simplify multi-die projects, and compress development schedules.

Resources

Resources

Lorem Ipsum has been the industry’s standard dummy text ever since the 1500s, when an printer.

- Chiplets: Opportunities and Challenges

- NoC-Centric System Performance for the Chiplet-Era with Platform Architect

- Optimizing Data Transport Architectures in RISC–V SoCs for AI/ML Applications

- Cache Coherency in Heterogeneous Systems

- Integration Challenges for RISC-V Designs

- Promises and Pitfalls of SoC Restructuring

- Scaling Performance in AI Systems

- Architecting the Future of Deep Learning Presentation

- Arm & Arteris AI and ISO 26262 Presentation

- Arm TechCon: Implementing ISO 26262 Compliant AI Systems-on-Chip with Arm and Arteris

- Automating the Generation of Scalable and Reusable FMEDA in Complex Systems-on-Chip (SoCs)

- Challenges Adopting Fault Injection to Support Safety Analysis in Complex SoCs

- Efficient Scaling of AI Accelerators Using NoC Tiling

- FMEDA Automation for Scalability and Reuse in Complex Systems on Chips (SoCs)

- Fundamentals of ISO 26262 Part 11 for Semiconductors

- Implementing Low-Power AI SoCs Using NoC Interconnect Technology

- Implementing Machine Learning & Neural Network Chip Architectures

- Is the Missing Safety Ingredient in Automotive AI Traceability?

- ISO 26262 System-on-Chip (SoC) Safety Analysis for ADAS and AV

- ISO 26262: FMEA before FMEDA

- ISO 26262: What to Expect From Your Chip or IP Provider

- Lessons Learned Integrating AI/ML Accelerators into Complex ISO 26262 Compliant Systems-on-Chip

- Routing Congestion: The Growing Cost of Wires

- Safety Considerations for Network-on-Chip (NoC) Development

- The Role of Networks-on-Chips Enabling AI/ML Silicon and Systems

- Tiled Approach to System Scaling

- Using Synopsys Z01X to Accelerate the Fault Injection Campaign of a Fully Configurable IP

- SemiWiki: How NoC Tiling Capability is Changing the Game for AI Development with Andy Nightingale

- EE Journal: Managing the Massive Data Throughput: AI-Based Designs and The Value of NoC Tiling

- Electronic Design: All About NoCs

- SemiWiki: The Impact of Arteris on Automotive and Beyond with Frank Schirrmeister

- SemiWiki: A Broad View of Design Architectures and the Role of the NoC with Arteris’ Michal Siwinski

- EE Journal: The Freedom to Innovate: Arteris and the Rise of RISC-V

- Fundamentals of Semiconductor ISO 26262 Certification: People, Process and Product

- How to Efficiently Achieve ASIL-D Compliance Using NoC Technology

- Mobileye Case Study: Using Arteris for ADAS

- Re-Architecting SoCs for the AI Era

- Routing Congestion: The Growing Cost of Wires

- Scalability – A Looming Problem in Safety Analysis

- Security in Artificial Intelligence

- Using Machine Learning for Characterizations of NoC Components

- Using Synopsys Z01X to Accelerate the Fault Injection Campaign of a Fully Configurable IP

- Using Virtual Prototypes to Improve the Traceability of Critical Embedded Systems Flow

- Making Cache Coherent SoC Design Easier with Ncore

Support and Training

Need Help?

Support and Services

Arteris provides world-class design support and services to our customers and partners.

Training

Unlock the full potential of Arteris products. Explore customized learning solutions designed to boost your expertise.

Arteris Academy

Learn at your own pace, on your schedule. Access our library of on-demand training modules and develop new skills today.

Latest News