Design & Reuse: Automating NoC Design to Tackle Rising SoC Complexity

- Andy Nightingale

- < 1 min read

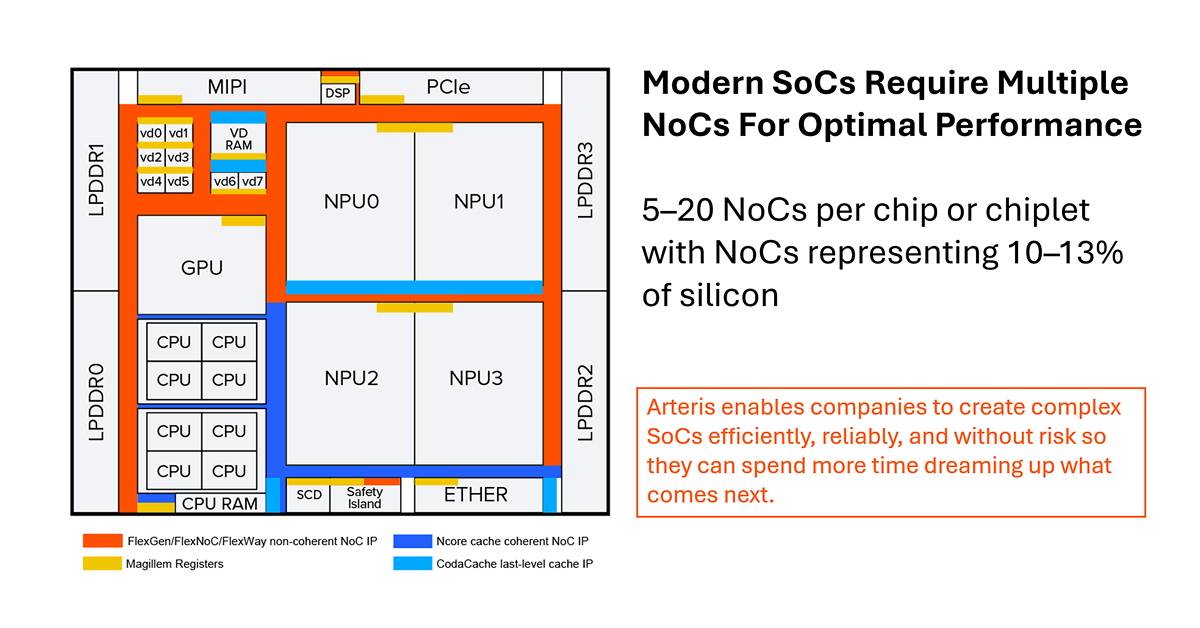

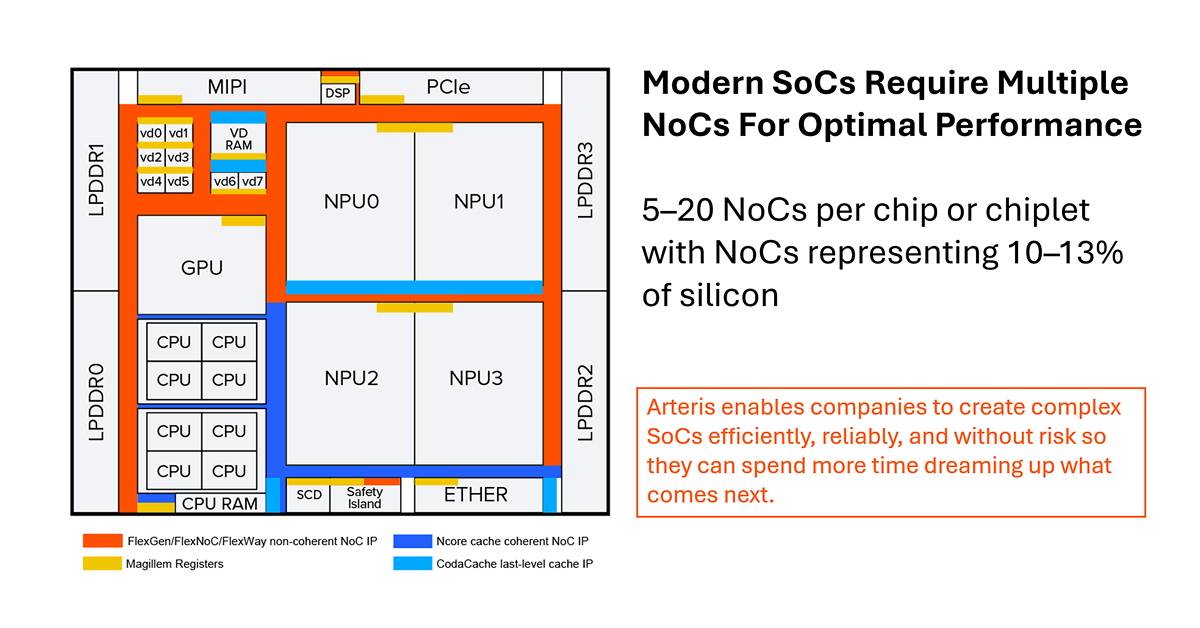

The semiconductor industry is experiencing unprecedented growth, driven by the increasing complexity of today’s chip designs. Advanced systems-on-chip (SoCs) now integrate over 300 intellectual property (IP) blocks, pushing design challenges to new levels. The rapid adoption of AI-driven automotive safety systems and the expansion of edge AI and IoT applications further highlight the demand for energy-efficient network-on-chip (NoC) solutions. This rising complexity requires a new level of scalability, especially for cutting-edge process nodes at 5nm, 3nm and beyond, where optimizing power, performance, and area (PPA) is essential.

Typically, SoCs now comprise between 5 to 20 individual NoC instances, occupying approximately 10-13% of the total silicon area. Current methodologies, combined with increasing register requirements, are becoming insufficient. As a result, designers face lengthy development cycles, repeated iterations, and significant schedule risks. Given these limitations, automated NoC generation offers a scalable solution to manage escalating design challenges.

Automated NoC Generation

To address these industry-wide issues, Arteris has developed FlexGen™ smart NoC IP, which uses advanced algorithms and AI-driven automation of NoC interconnect design and optimization. This technology reduces reliance on traditional manual design processes, enabling efficient management of modern SoC requirements.

By automating NoC design, teams can streamline development, achieving significant productivity gains while reducing manual effort. Typically, manual NoC designs require multiple adjustment cycles, often spanning weeks. With automation, design iterations can be completed in hours. This allows design teams to initiate physical layout earlier and evaluate architectural alternatives more rapidly. Shorter cycles directly translate into faster development timelines, accelerating time to market and mitigating schedule risks.

To read the full article on Design & Reuse, click here.